# **TOSHIBA MOS MEMORY PRODUCTS**

4096 WORD x 1 BIT STATIC RAM

N CHANNEL SILICON GATE DEPLETION LOAD

TMM315D-1

#### DESCRIPTION

TMM315D/TMM315D-1 are 4096 word x 1 bit read write memories operated with 5V single power supply. The memories are static in operation and require no clocks or refresh period. This device has two types in data access - address access and chip select access which are equal and very high speed. When  $\overline{\text{CS}}$  goes high, this device is deselected and changes into the low power standby mode automatically, and keep its state during the period that  $\overline{\text{CS}}$  is high. Accordingly, this device is suitable for use in

larger memory system which the majority of devices are deselected, and is suitable for use in cache memory required very high speed. TMM315D/TMM315D-1 are directly TTL compatible and its output can drive the TTL up to 5. TMM315D/TMM315D-1 are fabricated with N-channel silicon gate depletion load type technology for stable and high performance. The chip is mounted in the standard 18 pin package of 0.3 inch width for low cost purpose.

#### **FEATURES**

- Fully decoded 4096 word x 1 bit organization

- Static operation No clocks

- 5V single power supply

- Easy memory expansion CS input

- Standby feature  $-\overline{CS} = V_{IH}$

- I/O separate

- · Three state output

- Directly TTL compatible

## Current and Access time (Maximum value)

| PARAMETER               | TMM315D-1 | TMM3150 |

|-------------------------|-----------|---------|

| Active Current (Max.)   | 180 mA    | 160 mA  |

| Standby Current (Max.)  | 30 mA     | 20 mA   |

| Address Access time     | 55 ns     | 70 ns   |

| Chip select Access time | 55 ns     | 70 ns   |

- Pin to pin compatible i2147/i2147-3

- Inputs protected All inputs have protection against static charge.

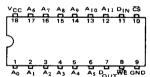

# PIN CONNECTION (TOP VIEW)

| $A_0 \sim A_5$                    | Row Address inputs    |

|-----------------------------------|-----------------------|

| A <sub>6</sub> ~ A <sub>1 1</sub> | Column Address inputs |

| DIN                               | Data input            |

| Роит                              | Data output           |

| CS                                | Chip select input     |

| WE                                | Write enable input    |

| Vcc/GND                           | Power supply          |

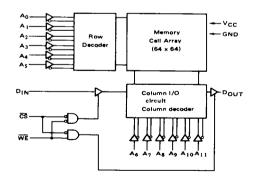

## **BLOCK DIAGRAM**

# OPERATION MODE

| <u>cs</u> | WE | Output         | Power   | Mode       |

|-----------|----|----------------|---------|------------|

| Н         |    | High-Impedance | Standby | Deselected |

| L         | Н  | Data out       | Active  | Read       |

| L         | L  | High-Impedance | Active  | Write      |

# MAXIMUM RATINGS

| SYMBOL            | ITEM                          | RATING     | UNIT     |

|-------------------|-------------------------------|------------|----------|

| Vcc               | Power supply voltage          | -1.5 ~ 7.0 | V        |

| VIN, OUT          | Input and output voltage      | -1.5~7.0   | V        |

| Topr              | Operating temperature         | 0~70       | •°C      |

| T <sub>strg</sub> | Storage temperature           | -55 ~ 150  | °C       |

| Tsolder           | Soldering temperature · time  | 260 · 10   | °C · sec |

| PD                | Power dissipation (Ta = 70°C) | 1.0        | w        |

| lout              | DC output current             | 20         | mA       |

# DE CHEF ATENG CONDITIONS

| SYMBOL | PARAMETER            | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|--------|----------------------|------------|------|------|------|------|

| ViH    | Input high voltage   |            | 2.0  |      | 6.0  | V    |

| VIL    | Input low voltage    |            | -1.0 | _    | 0.8  | V    |

| Vcc    | Power supply voltage |            | 4.5  | 5.0  | 5.5  | V    |

# DEPOS HEREING CHARLES ERREITES

Ta =  $0 \sim 70^{\circ}$ C, Vcc = 5.0V± 10%,unless otherwise noted

| SYMBOL | PARAMETER               | CONDITIONS                                                                             |            | MIN. | TYP.   | MAX. | UNIT |

|--------|-------------------------|----------------------------------------------------------------------------------------|------------|------|--------|------|------|

| Voн    | Output high voltage     | source = -                                                                             | 4.0 mA     | 2.4  |        |      | V    |

| Vol    | Output low voltage      | Isink = 8 m                                                                            | Δ          |      | -      | 0.4  | V    |

| Юн     | Output high current     | Von = 2                                                                                | VoH = 2.4V |      | -      |      | mA   |

| loL    | Output low current      | V <sub>OL</sub> = 0.4V                                                                 |            | 8.0  |        | _    | mA   |

| ILI    | Input leakage current   | VIN = 0 ~ VCC                                                                          |            | _    | ± 0.01 | ± 10 | μА   |

| lLO    | Output leakage current  | $V_{OUT} = 0 \sim 4.5V$<br>$\overline{CS} = V_{IH} \text{ or } \overline{WE} = V_{IL}$ |            | _    | ±0.1   | ± 50 | μА   |

| lcc    | Operating current       | CS = VIL                                                                               | TMM315D    | -    | _      | 160  | mA   |

|        | Operating current       | output open                                                                            | TMM315D-1  |      | -      | 180  | mA   |

| ISB    | Standby current         | CS = VIH                                                                               | TMM315D    |      | _      | 20   | mA   |

| 130    | Standby current         | output open                                                                            | TMM315D-1  | _    | _      | 30   | mA   |

| ISBP   | Peak power on current   | CS = VIH                                                                               | TMM315D    | _    | _      | 50   | mA   |

| 1301   | T can power off current | during power on                                                                        | TMM315D-1  | _    | _      | 70   | mA   |

<sup>\*</sup> Typical values are at Vcc = 5.0V, Ta = 25°C.

#### A.C. CHARACTERISTICS

Ta =  $0 \sim 70$  °C, V<sub>CC</sub> = 5V± 10%,unless otherwise noted.

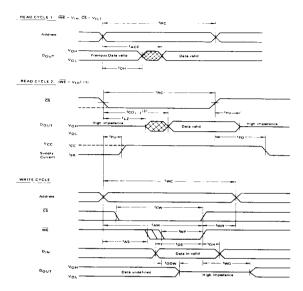

#### READ CYCLE

| SYMBOL PA        | PARAMETER                            | TMM  | 315D-1 | TMM315D |            |      |

|------------------|--------------------------------------|------|--------|---------|------------|------|

|                  |                                      | MIN. | MAX.   | MIN.    | MAX.       | UNIT |

| trc              | Read cycle time                      | 55   | _      | 70      | · -        | пs   |

| tACC             | Address access time                  |      | 55     |         | 70         | ns   |

| tco <sub>1</sub> | Chip select access time 1            | _    | 55     | -       | 70         | ns   |

| tCO2             | Chip select access time 2            | _    | 65     | _       | 80         | ns   |

| tон              | Output hold from address change      | 5    | T -    | 5       | ·          | ns   |

| tLZ              | Chip selection to output in low Z    | 10   |        | 10      | †          | ns   |

| tHZ              | Chip deselection to output in high Z | 0    | 40     | 0       | 40         | ns   |

| tPU              | Chip selection to power up time      | 0    |        | 0       | † <u>-</u> | ns   |

| tPD              | Chip deselection to power down time  |      | 30     | _       | 30         | ns   |

#### . WRITE CYCLE

| SYMBOL | PARAMETER                        | TMM  | TMM315D-1 |      | TMM315D |      |

|--------|----------------------------------|------|-----------|------|---------|------|

|        | FANAMETER                        | MIN. | MAX.      | MIN. | MAX.    | UNIT |

| twc    | Write cycle time                 | 55   | _         | 70   | -       | ns   |

| tcw    | Chip selection to end of write   | 45   | _         | 55   | _       | ns   |

| taw    | Address valid to end of write    | 45   | -         | 55   | _       | ns   |

| tAS    | Address set up time              | 0    | -         | 0    |         | ns   |

| twp    | Write pulse width                | 35   | i –       | 40   | _       | ns   |

| twn    | Write recovery time              | 10   | 1         | 15   |         | ns   |

| tos    | Data set up time                 | 25   | 1 -       | 30   | -       | ns   |

| tDH    | Data hold time                   | 10   | T -       | 10   | -       | ns   |

| topw   | Write enable to output in high Z | 0    | 30        | 0    | 35      | ns   |

| two    | Output active from end of write  | 0    |           | 0    | _       | ns   |

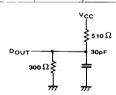

#### • AC TEST CONDITIONS

| Input pulse levels                       | 0~3.5V   |

|------------------------------------------|----------|

| Input rise and fall times                | 10 ns    |

| Input and output timing reference levels | 1.5V     |

| Output load                              | See Fig. |

Fig. 1 Output load

| SYMBOL | PARAMETER          | MAX. | UNIT |

|--------|--------------------|------|------|

| CIN    | Input capacitance  | 5    | ρF   |

| Cout   | Output capacitance | 7    | ρF   |

This parameter is periodically sampled and is not 100% tested.

# TOSHIBA

### **TIMING WAVEFORMS**

Note: (1) Addresses are to valid prior to or coincident with CS transition low.

(2) tCO1: Chip is deselected for a time that is greater than 55 ns prior to selection. tCO2: Chip is desalected for a time that is less than 55 ns prior to selection.

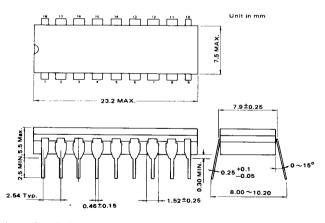

Note: 1. Each lead pitch is 2.54 mm. All leads are located within 0.25 mm of their true longitudinal position with respect to No. 1 and No. 18 leads.

2. All dimensions are in millimeters.

Toshiba does not assume any responsibility for use of any circultry described; no circult patent licenses are implied, and Toshiba reserves the right, at any time without notice, to change said circuitry.

© Aug., 1980 Toshiba Corporation