# CMOS Technology

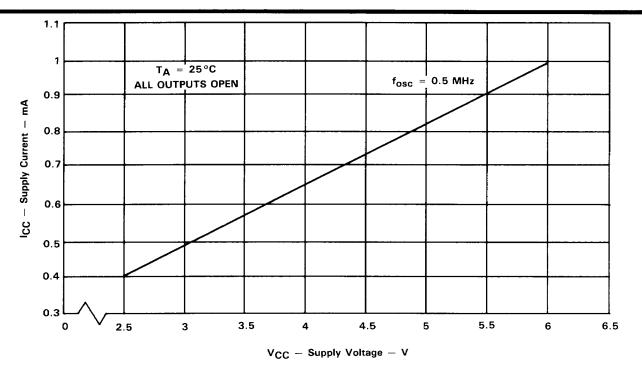

### Wide Operating Range

- Voltage (VCC) 2.5 V to 6.0 V

- Frequency 0.5 MHz to 6.0 MHz

- Temperature -40 °C to 85 °C

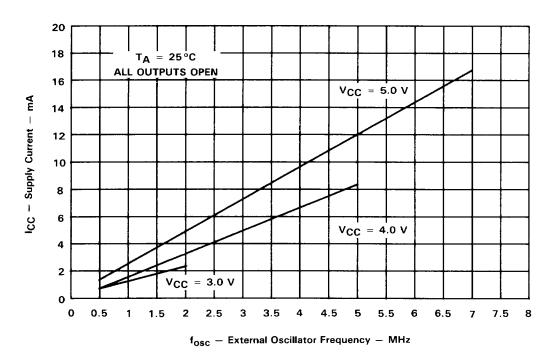

### • Low Operating Current

- 15 mA Typical Operating Current at 6 MHz

- Wake-Up Mode for Power Savings

# • Flexible Memory Configurations

- 256-Byte On-Chip RAM Register File

- Memory-Mapped Ports for Easy Addressing

- 4K-Byte On-Chip ROM (TMS70C42)

- Memory Expansion to 64K Bytes

- TMS70C02 ROMless Microprocessor

- 32 CMOS Compatible I/O Pins (TMS70C42)

- 24 Bidirectional Pins

- 8 Output Pins

### Three On-Chip Timers:

- Two 16-Bit with 5-Bit Prescale and 16-Bit Capture Latch, Cascadable

- Timer Outputs on Timer 1 and Timer 2

- One 8-Bit with 2-Bit Prescale

- Internal Interrupt with Automatic Timer Reload

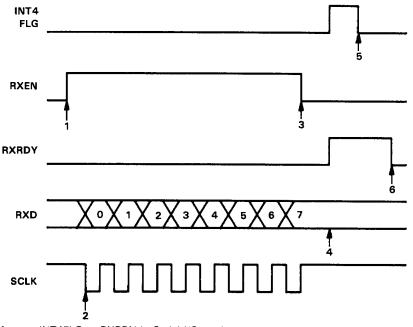

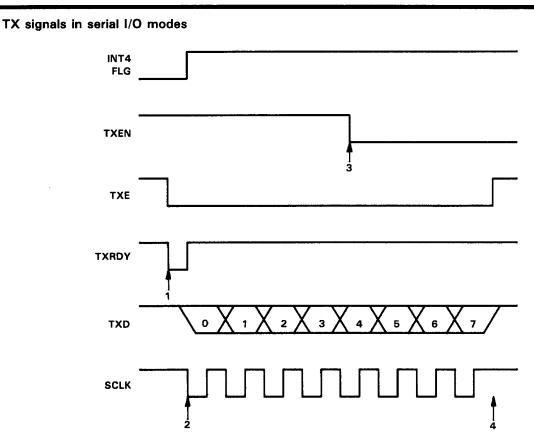

### On-Chip Serial Port

- Flexible Data Protocols

- Internal or External Baud Rate Generator

- Error Detection Flags

- Separate Baud Rate Generator or Usable as a Third General Purpose Timer

- Asynchronous, Synchronous, and Serial Modes

- Two Multiprocessor Communication Formats

# • Flexible Interrupt Handling:

- External Interrupts Programmable for Edge or Edge/Level Triggering

- External Interrupts Programmable for Rising or Falling Edge Detection

- Software Calls through Interrupt Vectors

- Software Monitoring of Interrupt Status

- Precise Interrupt Timing through Capture Latch

- Priority Servicing of Simultaneous Interrupts

- Global and Individual Interrupt Masking

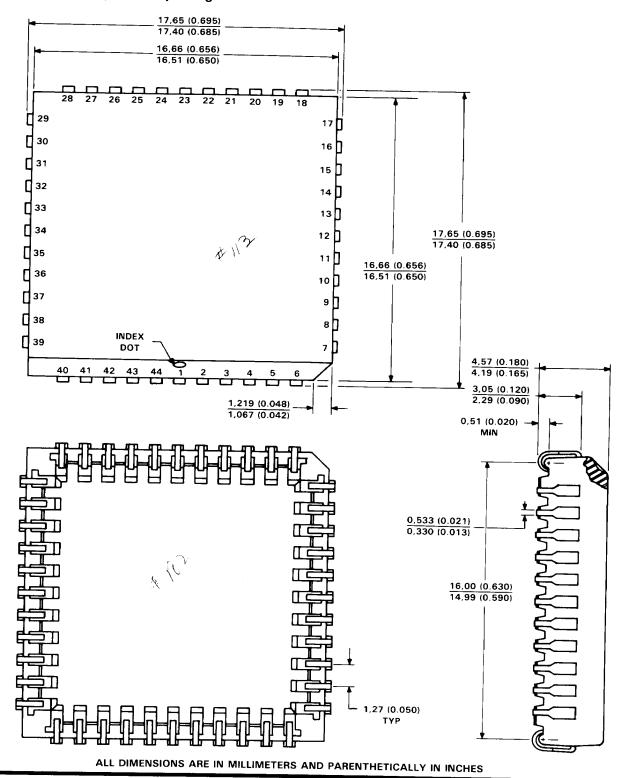

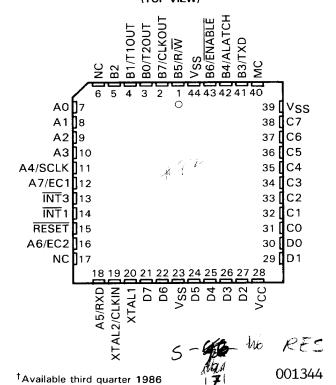

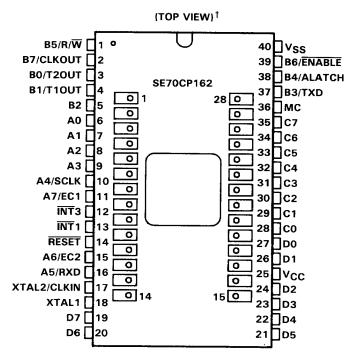

FN PACKAGE<sup>†</sup>

(TOP VIEW)

T 1344

TI

1

Copyright © 1986, Texas Instruments Incorporated

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

# TMS70C42/TMS70C02 8-BIT CMOS MICROCOMPUTERS

- Additional Member of TMS7000 Family

- Register-to-Register Architecture

- Instructions Set Compatible with All TMS7000 Family Members

- Eight Powerful Addressing Formats Including:

Register-to-Register Arithmetic Indirect Addressing Indexed and Indirect Branches and Calls

- Development Support

- Piggyback Prototyping Device, SE70CP162

- Low Cost Evaluation Module

- Full Feature Development System

- Assembler/Linker Cross Support for Popular Hosts

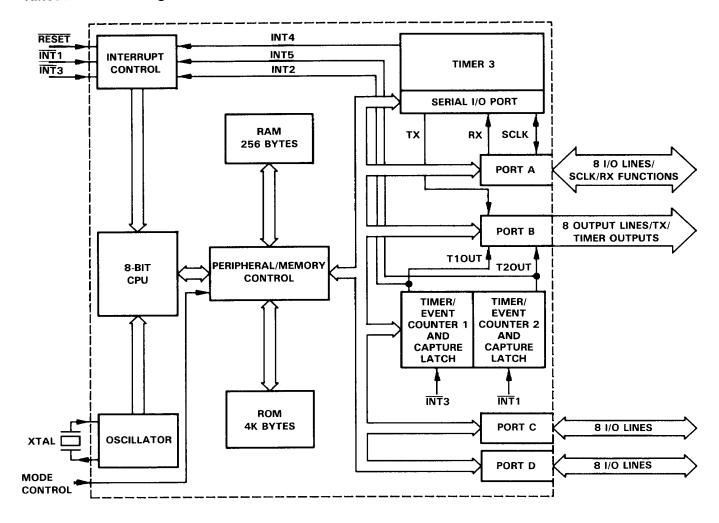

### description

The TMS70C42 is an 8-bit CMOS microcomputer that contains 4K bytes of on-chip ROM, 256 bytes of on-chip RAM, a flexible serial port, three timers, and 32 I/O lines. The TMS70C42 features advanced register-to-register architecture that allows direct arithmetic and logical operations without requiring the use of an accumulator (e.g., ADD, R24, R245; add register 24 to register 245 and store the result in register 245).

The TMS70C02 is the microprocessor version of the TMS70C42, having no on-chip ROM. The TMS70C02 uses 20 of the I/O lines for address, data, and bus control. The TMS70C02 can be used in large ROM applications and typical microcomputer applications that take advantage of on-chip features such as the UART, RAM, and timers.

Unless otherwise noted, the use of the term TMS70C42 in this document refers to both the TMS70C42 and TMS70C02.

The TMS70C42 is a low-cost microcomputer that is ideal for low power or battery powered operations. The high noise immunity, wide operation conditions and ranges of CMOS, and high performance CPU and internal peripherals allow flexible system designs in industrial, automotive, computer, and telecom applications.

The 16-bit timers, with their associated 16-bit capture latch and timer outputs, simplify A/D conversions, pulse width measurements, and other time-critical application designs.

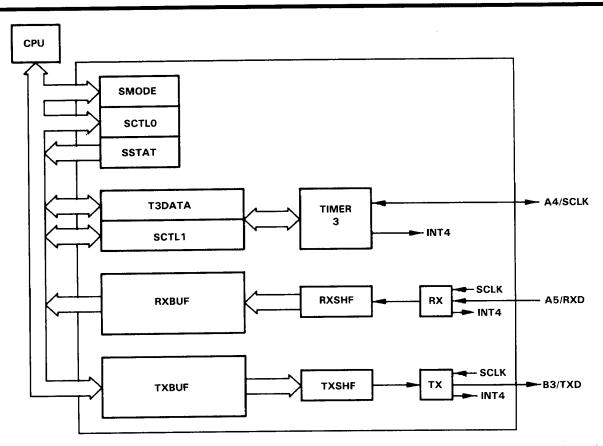

The unique serial port has many powerful features allowing operation in various selectable protocols. It also supports direct networking for processor-to-processor communications.

When power consumption is critical, the TMS70C42 can idle selectable sections of the microcomputer (e.g., Timer 1, Timer 2, or UART) and use power only where needed. Also, the entire processor can be halted while retaining the 256 bytes of internal RAM over a wide range of supply voltages.

The TMS70C42 instruction set is compatible with that of all TMS7000 family members, allowing easy transition between members.

# functional block diagram

# TMS70C42/TMS70C02 8-BIT CMOS MICROCOMPUTERS

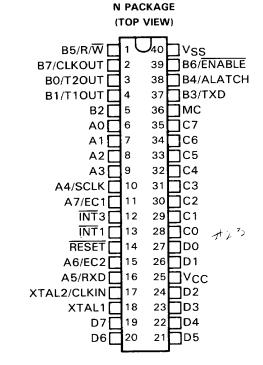

# pin descriptions

|                 | PIN       |            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-----------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER          |           | I/O        | DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NAME            | N PACKAGE | FN PACKAGE |             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AO(LSB)         | 6         | 7          | I/O         | Port A is a bidirectional data port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A1              | 7         | 8          | I/O         | and a state of the |

| A2              | 8         | 9          | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| А3              | 9         | 10         | 1/0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A4/SCLK         | 10        | 11         | I/O         | Data I/O/Serial port clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A5/RXD          | 16        | 18         | I/O         | Data I/O/Serial port input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A6/EC2          | 15        | 16         | 1/0         | Data I/O/Timer 2 event counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A7/EC1          | 11        | 12         | I/O         | Data I/O/Timer 1 event counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BO/T2OUT        | 3         | 3          | 0           | Data output/Timer 2 underflow toggles output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B1/T1OUT        | 4         | 4          | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B2              | 5         | 5          | 0           | Data output/Timer 1 underflow toggles output  Data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B3/TXD          | 37        | 41         | 0           | Data output  Data output/Serial port output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B4/ALATCH       | 38        | 42         | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B5/R/W          | 1         | 1          | 0           | Data output/Memory interface address latch strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B6/ENABLE       | 39        | 43         | 0           | Data output/Memory interface Read/Write signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B7/CLKOUT       | 2         | 2          | 0           | Data output/Memory interface enable strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BITCEROOT       |           | 2          | U           | Data output/Memory interface clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CO              | 28        | 31         | I/O         | Port C is a bidirectional data port. In Peripheral Expansion, Full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C1              | 29        | 32         | I/O         | Expansion, and Microprocessor modes, Port C is a multiplexed low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| C2              | 30        | 33         | I/O         | address and data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C3              | 31        | 34         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C4              | 32        | 35         | 1/0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C5              | 33        | 36         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C6              | 34        | 37         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C7              | 35        | 38         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DO              | 27        | 30         | I/O         | Port D is a bidirectional data port. In Full Expansion and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D1              | 26        | 29         | I/O         | Microprocessor modes, Port D is the high address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D2              | 24        | 27         | 1/0         | The state of the s |

| D3              | 23        | 26         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D4              | 22        | 25         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D5              | 21        | 24         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D6              | 20        | 22         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

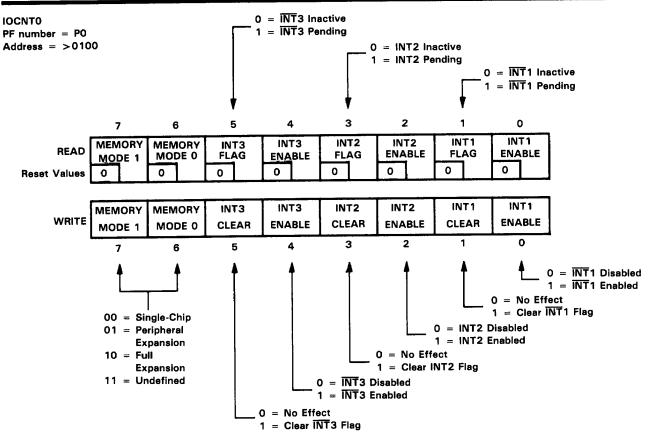

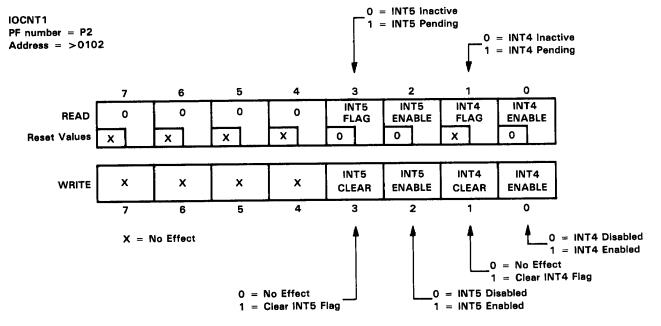

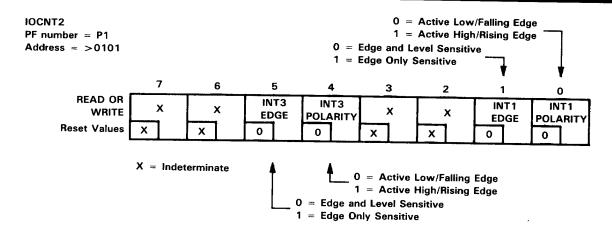

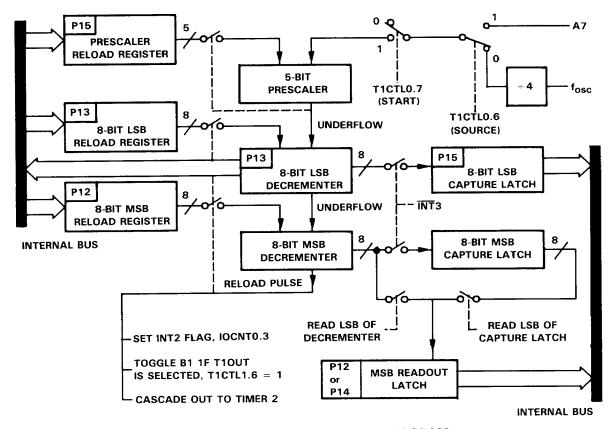

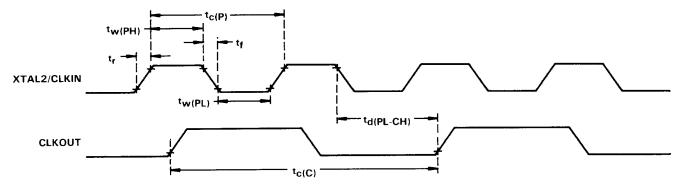

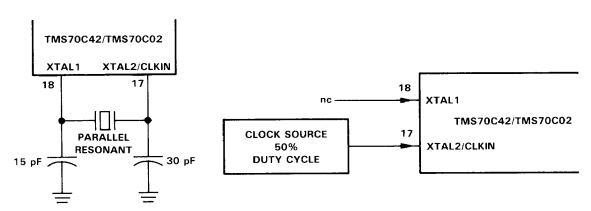

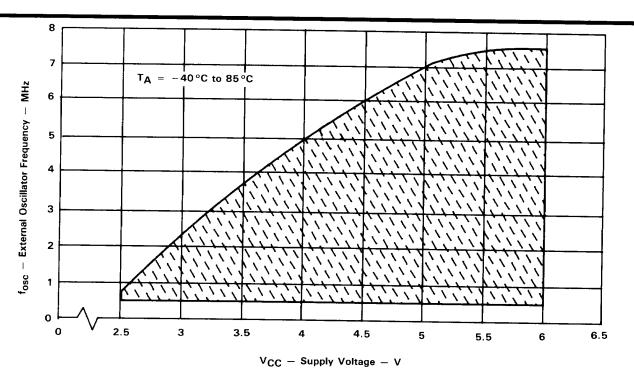

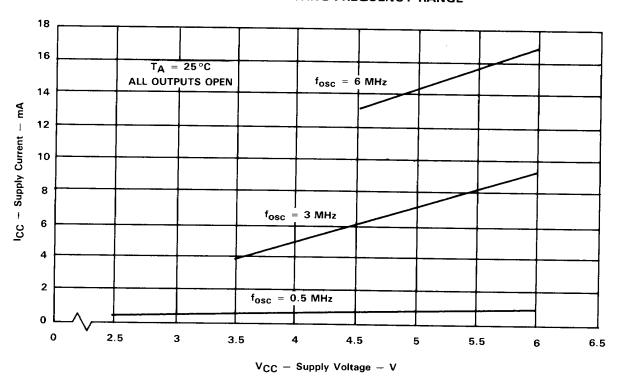

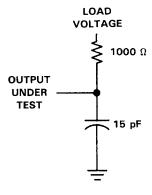

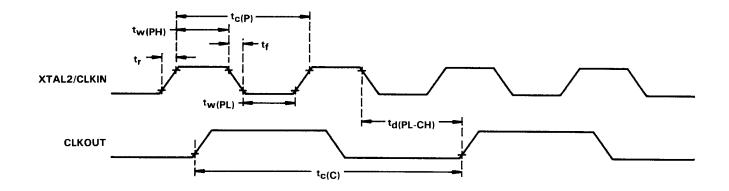

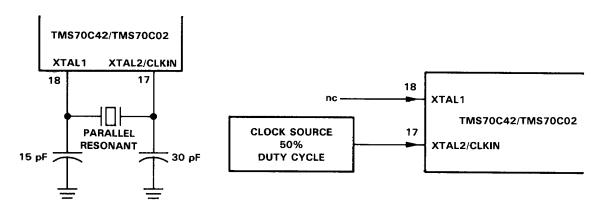

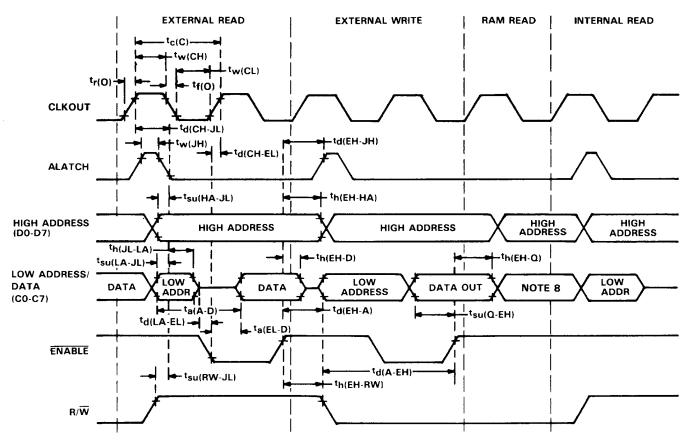

| D7              | 19        | 21         | I/O         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |